硬件学习之数字电路(三)

这章讲锁存器

锁存器

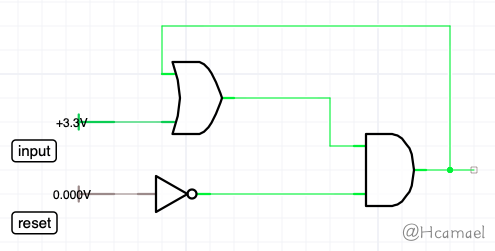

当input输入1以后,输出就会一直输出1,所以才叫做锁存器,只有在设置了reset的时候,输出才会被设置成0,通过该方法来修改输出的值。

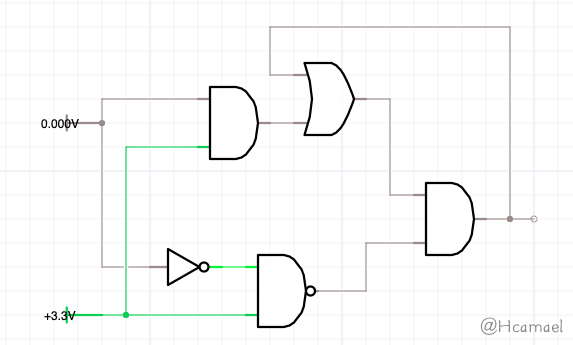

还有一种更复杂的,把reset位更改为write位:

只有在write位为1的使用,输入才能影响到输出

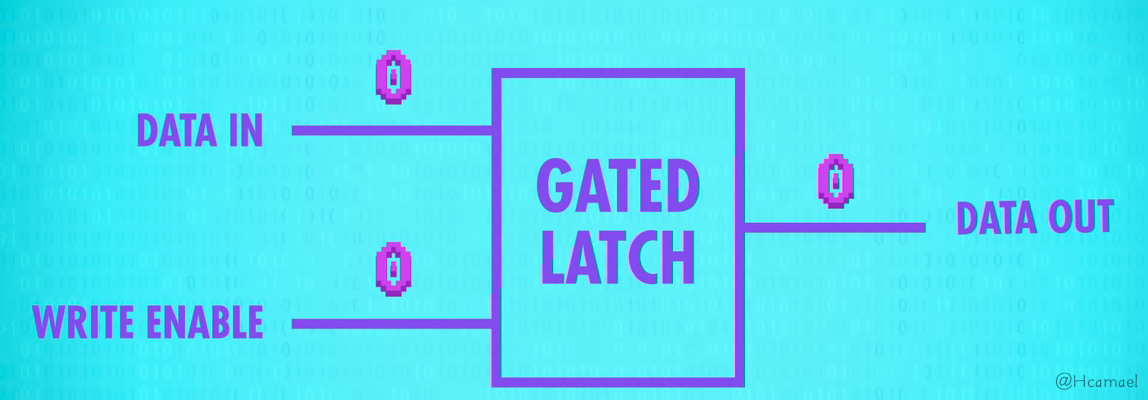

为了更方便的造出更复杂的元件,我们把这个锁存器进行封装:

多路复用器

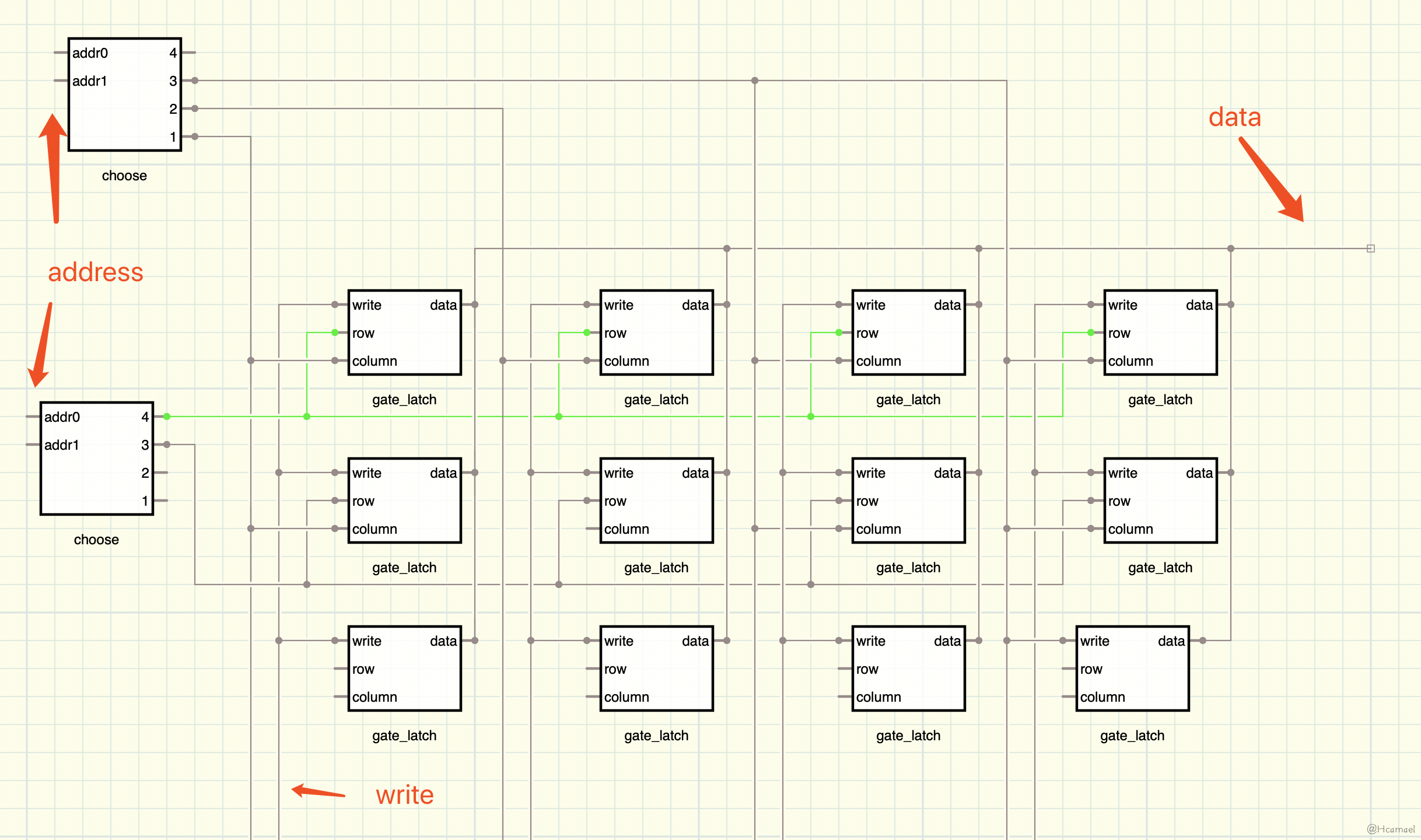

把锁存器按照4 * 4的矩阵排列,得到4bit * 4bit的RAM

内存地址的寻址范围是0b0000 - 0b1111

可以把4bit的地址线分成2bit的横向地址线和2bit的纵向地址线

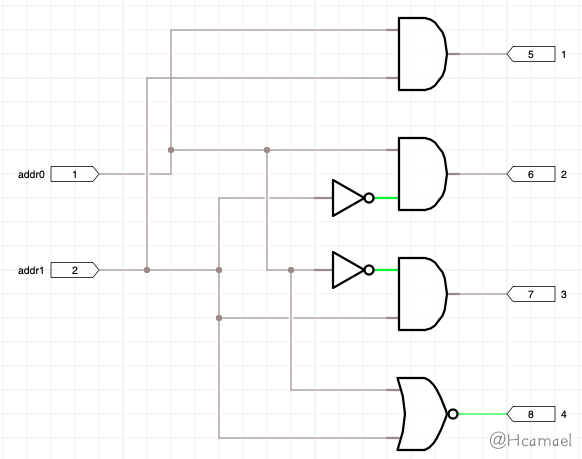

还需要一个多路复用器,我们先来想想怎么实现一下多路复用器。一共两2bit的横向地址线,所以有2bit的输入,横向有4列,所以要有4根输出,输入输出应该有如下对应关系:

| Addr0 | Addr1 | Output0 | Output1 | Output2 | output3 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

一种简单的实现方法如下:

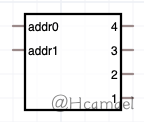

对上面的电路进行封装:

RAM

先来想想我们的RAM都有哪些输入输出?

首先是地址线,因为是 4*4bit的RAM,所以有4bit的地址线

肯定要有一根可写地址线

最后就是数据线,读写可以共用数据线,因为只是4*4bit的RAM,所以我们只拿1bit的数据线

综上,对于一个4*4bit的RAM最少需要6根外部接口

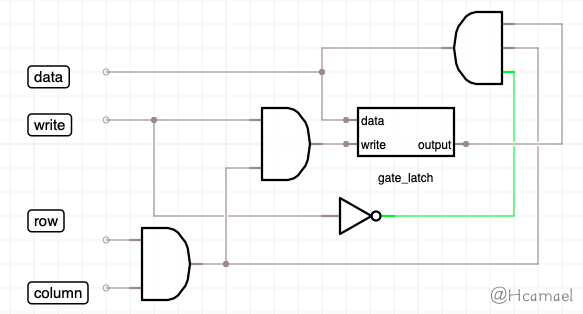

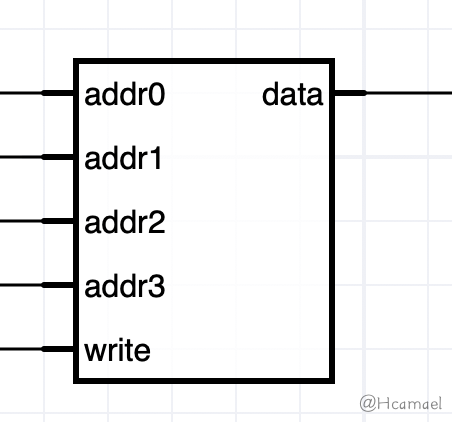

要设计一个RAM,我们先从小的来看,对于锁存器,要有多少根接口呢?因为4bit的地址线,最终是选择到1个锁存器,所以从RAM到锁存器,地址线从4根缩减到2根,所以锁存器只需要4根线。如下图所示:

只有当行,列都被选中的时候,写和输出才能被开启。只有当没开启写的情况下,才能开启输出。

首先把所有锁存器的数据线和可写线连起来,他们共享同一根数据线和可写线。

这样就成功设计了一个简单的RAM,但是和我们平常使用的还是有点差距,上面的RAM每个地址只能储存1bit的数据,但是平常使用的RAM一个地址能储存1字节的数据。

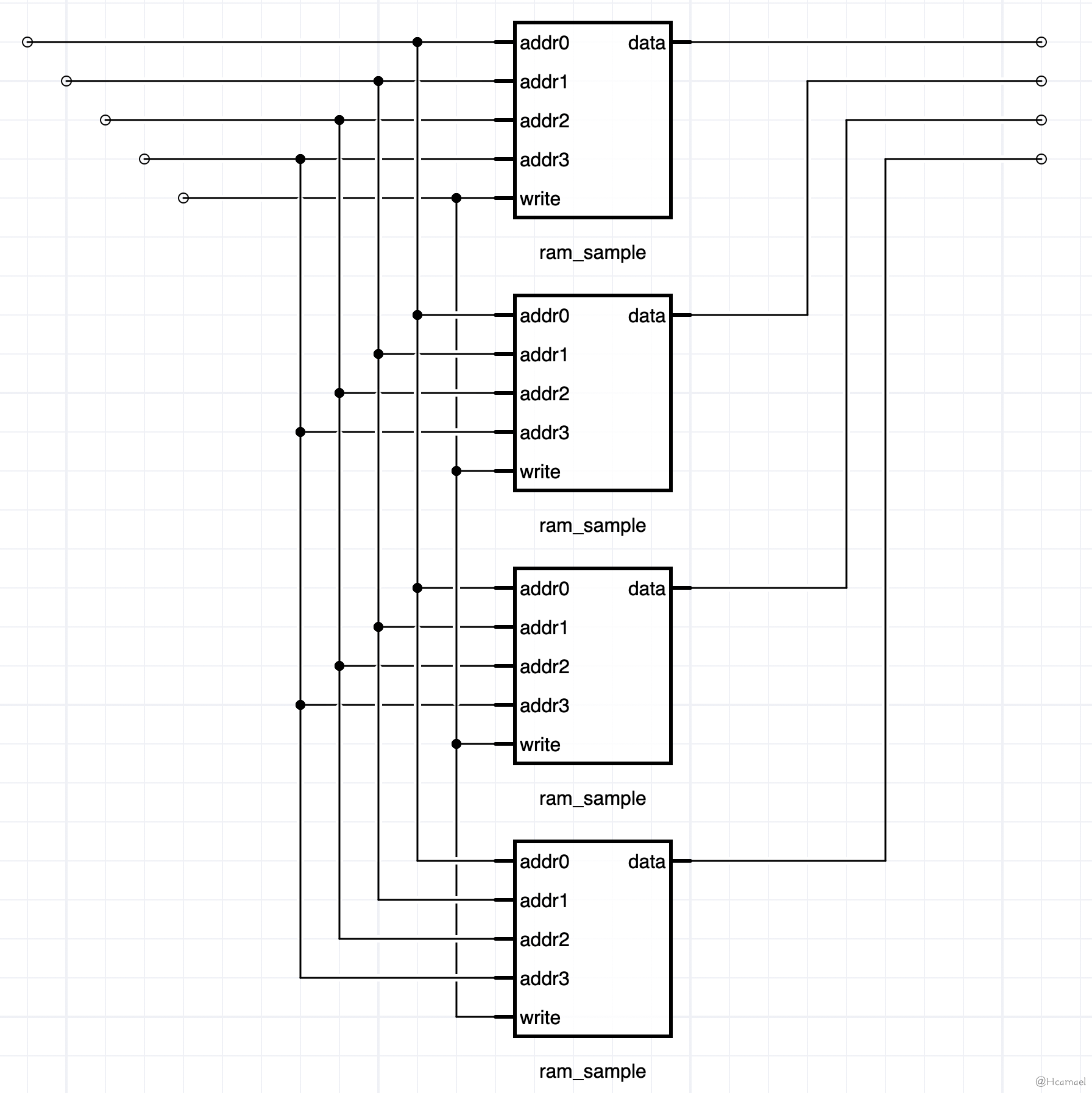

储存数据量差了8倍,只要把电子器件同样增加8倍就好了,我们首先将上面的RAM再进行一次封装:

将上图的基本单元进行扩展,得到下图的结构:

PS:只是举例,8个不好做图,就举例4个了

仍然是4根地址线,1根可写线,但是数据线扩展到了4根

硬件学习之数字电路(三)